Informatik - Skript zum Unterricht

(I) Hardware

- 0. Einführung

- 1. Begriffsbestimmung

- 2. Die Wurzeln der Informatik

- 3. Grundaufbau

- 4. Verarbeitungseinheit

- 5. externe Datenträger

- 6. Von der Hard- zur Software

4. Verarbeitungseinheit

4.1 Grundschema der Zentralen Verarbeitungseinheit

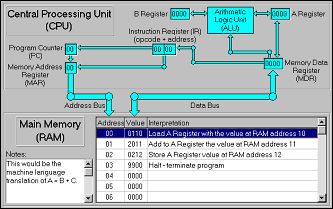

Das Bild zeigt den schematischen Grundaufbau der Verarbeitungseinheit (Einkernprozessor).

Der Rechenkern (engl. central processing unit; Prozessor) umfasst alle Funktionseinheiten, um Befehle

interpretieren und auswerten zu können. Er unterteilt sich in das Rechen- und Steuerwerk (Taktgeber, Datenaustausch) und in

einen Ein-/Ausgabeprozessor, der die Kommunikation mit Speichern, Peripheriegeräten u.a. herstellt.

Der Rechenkern verfügt nur über begrenzten Speicher (z.B. einige Register).

Das Rechenwerk (ALU - arithmetic logical unit) ist führt die arithmetischen und logischen Berechnungen durch. Die Minimaloperationen (Arithmetisch: Addition ADD, Logisch: Negation NOT und Konjunktion AND), die es durchführen kann, werden durch weitere Operationen (Subtraktion SUB) ergänzt. Andere Rechenoperationen können aus den Grundrechenarten abgeleitet werden.

Das Steuerwerk ist der Kern des Prozessors. Es ist für die Steuerung der Reihenfolge der Abarbeitung der Befehle und die Verteilung dieser an die anderen Funktionseinheiten des Prozessors zuständig.

Die Register sind flüchtige Speicherzellen des Prozessors, auf die dieser durch die kurze Anbindung sehr schnell zugreifen kann. Die Register werden zum Zwischenspeichern von Befehlen, Speicheradressen, Rechenoperanden und Ein- und Ausgabewerten verwendet.

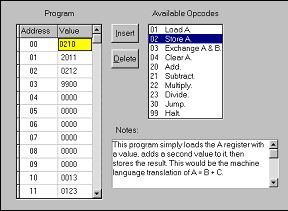

Beispiel für eine Addition in Maschinensprache mit schematischer Darstellung:

4.2 Mikroprozessortypen (Einkernprozessoren)

Die Firma Intel stellte 1971 den 4 Bit Microprozessor 4004 vor. Dieser kam in Taschenrechner und Registrierkassen zum Einsatz.

Er wurde von Ted Hoff (Intel) für Busicom (Japan) entwickelt und besaß 2.300 Transistoren, 604 adressierbare Byte und

verarbeitete 60.000 Befehle je Sekunde (0,06 MIPS) bei einer Taktfrequenz von 0,108 MHz.

Prozessoren wurden und werden neben Intel und AMD von der Firma Motorola und anderen produziert. Von Motorola ist hierbei die 8 Bit CPU 6510 (Weiterentwicklung des 6502) für den Computer Commodore C64 (1984) legendär.

Diese Tabellen erheben keinen Anspruch auf Vollständigkeit. Sie können auch die rasante Entwicklung der Prozessoren nicht

annähernd abbilden. Sie sollen nur die spannende Entwicklung im Bereich der Einkernprozessoren der Vergangenheit etwas näher bringen.

Deshalb wird an dieser Stelle auf die aktuelle Entwicklung - besonders nach dem Pentium IV - nicht weiter eingegangen.

So wird bewusst auf die Mehrkernprozessoren verzichtet.

4.2.1 Prozessoren der Firma Motorola und weiterer Firmen

| Prozessor | 6800 | 68000 | 68010/68020 | 68030 | 68040 |

| Einführung | 1974 | 1979 | 1984 | 1986 | 1989 |

| Verarbeitungsbreite | 8 Bit | 16 Bit | 32 Bit | 32 Bit, (CoPro ext.) | 32 Bit, (mit CoPro) |

| Computertyp | Tektronix 4051, ca. 1 MHz Taktfrequenz | Amiga 500, Atari ST | Atari ST, Amiga 2500 | Atari Falcon 030 | Amiga 4000, Falcon 040 |

Weitere, häufig auftretende bzw. historische Mikroprozessoren, die in verschiedenen Computertypen Verwendung finden (Auszug)

| Prozessor | Verarbeitungsbreite | Computertyp | Bemerkung |

| 4004 | 4 Bit | Taschenrechner Registrierkassen | 1971 von Ted Hoff (Intel) für Busicom (Japan) entwickelt, 2300 Transistoren, 604 Byte adressierbar, 60.000 Befehle/s (0,06 MIPS), 0,108 MHz |

| Z 80 | 8 Bit | C 128, KC85/X, ZX81 | 1976, Zilog ('85), kompatibel zum 8080; CP/M. |

| Sharp LR 35902 | 8 Bit | GameBoy | 4,19 MHz, dem Z80 sehr ähnlich |

| 6502 | 8 Bit | Lerncomputer KIM-1PET, VC 20, Apple I | MOS Industries (wurde 1976 von CBM übernommen) |

| 6510 | 8 Bit | C 64 | Weiterentw. des 6502 |

| 8086 | 16 Bit | IBM-PC 1981 | Urvater des PC, 64KB RAM, Kassettenlaufwerk |

| ARM 2 (Arcorn Risc Machine) | 32 Bit | Arcorn Archimedes A300 | 1987, 8MHz, 1MB RAM, RISC OS ARTHUR |

| ARM 610 | 32 Bit | Acorn Risc PC 600, Apple "Newton" | 20-33 MHz, Risc-Architektur |

| ARM 710T | 32 Bit | Psion "Revo" (PDA), Psion "5mx Pro" | 36,5 MHz, 8MB RAM (Revo Plus: 16MB), 16MB ROM, Betriebssystem EPOC 32 |

| Psion "5mx Pro" | 36,5 MHz, 32 MB RAM | ||

| ARM XScale | 32 Bit | Palm Tungsten T3 | 400 MHz Intel CPU, Palm OS 5.2.1, 16 MB Flash-RAM, 64 MB ROM |

| ARM 1176 | 32 Bit | iPhone | 412 MHz (G3: 600 MHZ), 120 MHz PowerVR-MBX GPU |

| ARM Cortex | 32 Bit | Palm pre, iPad | Hauptprozessor (RISC, Cortex A8-Kern) im "System on a Chip" (intern ergänzt um GPU, RAM

) z.B. im OMAP 3430 von TI (Palm pre) und im Apple A4 (iPad) |

| M68EC000 (Motorola VZ Dragonball, 68000er-Serie) | 32 Bit | Palm m515 | 33 MHz, 8MB Flash-ROM, 16MB RAM, Erweiterung über SD- bzw. MultiMediaCard, Palm OS 4.1 |

| MPC604r | 64 Bit | Power PC, IBM | 250-375 MHz, CPU von Motorola |

| R5000 bzw. R10000 | 64 Bit | O2, Silicon Graphics | 64 Bit Risc Prozessor, Toy Story, Jurassic Park |

| Alpha 26411 | 64 Bit | DECDigital Equipment | 433-500 MHz |

| 970MP G5 | 64 Bit | Apple iMac | 1,4 bis 2,5 GHz, Motorola, Power Mac G5, |

| AMD Opteron | 64 Bit | AMD-Server | 2003, SledgeHammer |

4.2.2 Prozessoren der Firmen Intel und AMD (Auszug)

| Prozessor | 4004 | 8008 | 8080 | 8086 |

| Einführung | 1971 | 1972 | 1974 | 1978 |

| Verarbeitungsbreite | 4 Bit | 8 Bit | 8 Bit | 16 Bit |

| Datenbusbreite | 4 Bit | 8 Bit | 8 Bit | 16 Bit |

| Adressbusbreite | 8 Bit | 16 Bit | 16 Bit | 20 Bit |

| phys. Adressraum | 604 Byte | 64 KB | 64 KB | 1 MB |

| (max.) Taktfrequenz | 108 kHz | 1 MHz | 1 MHz | 10 MHz |

| Prozessor | 8088 | 80186 | 80286 | 80486DX |

| Einführung | 1979 | 1982 | 1982 | 1989 |

| Verarbeitungsbreite | 16 Bit | 16 Bit | 16 Bit | 32 Bit |

| Datenbusbreite | 8 Bit | 16 Bit | 16 Bit | 32 Bit |

| Adressbusbreite | 20 Bit | 20 Bit | 24 Bit | 32 Bit |

| phys. Adressraum | 1 MB | 1 MB | 16 MB | 4 GB |

| (max.) Taktfrequenz | 10 MHz | 10 MHz | 16 MHz | 133 MHz |

| Prozessor | Pentium | Pent. II | Pent. III | Pent. IV | Pent. Extr. Edit. | AMD Athlon 64 |

| Einführung | 1992 | 1997 | 1999 | 2000 | 2005 | 2003 |

| Verarbeitungsbreite | 32 Bit | 32 Bit | 32 Bit | 32 Bit | 32 Bit | 64 Bit |

| Datenbusbreite | 64 Bit | 64 Bit | 64 Bit | 64 Bit | 64 Bit | |

| Adressbusbreite | 32 Bit | 64 Bit | 64 Bit | 64 Bit | 64 Bit | |

| phys. Adressraum | 16 GB | 16 GB | 16 GB | 16 GB | 40 Bit | |

| (max.) Taktfrequenz | 200 MHz | 500 MHz | 1,8 GHz | 3,8 GHz | 3,46 GHz | 3,6 GHz |

Stand 03/2007

Quellen:

PC Professionell 12/97 S.138 ff.

PC-Magazin 1998, Der Grosse Prozessor Guide

Jahresarbeit "CPU", Thomas Bradtke, 1999, Friedrich-Schiller-Gymnasium Weimar

Vortrag "Prozessoren", Thomas Eixner, 1999, Friedrich-Schiller-Gymnasium Weimar

www.computer-archiv.de

www.intel.de

de.wikipedia.org

4.3 Bussysteme

Damit der Mikroprozessor Befehle und Daten vom Arbeitsspeicher verarbeiten kann, müssen diese durch ein Verbindungsmittel zum Prozessor selbst übertragen werden. Weiterhin muss eine Verbindung zu den Ein- und Ausgabegeräten vorhanden sein, um mit dem Anwender in kommunizieren zu können.

Ein Bus ist die Zusammenfassung einer Vielzahl von parallelen Leitungen, an die mehrere Funktionsblöcke oder Komponenten eines Computers angeschlossen sind. Zumeist (beim IBM komp. PC) ist ein Bus untergliedert in Datenbus, Adressbus und Steuerbus.

Mit dem ersten IBM-PC wurde ein Bussystem eingeführt, das über insgesamt 62 Leitungen - darunter 20 Adressleitungen (220=1Mbyte Adressraum) und 8 Datenleitungen (8 Bit = 1 Byte wird gleichzeitig übertragen) - verfügte.

| Bussysteme im IBM-PC und seinen Nachfolgern |

Datenbusbreite | Adressbusbreite | Adressraum |

| PC-Bus | 8 Bit | 20 Bit | 220 = 1 MByte |

| ISA-Bus (AT-Bus) | 16 Bit | 24 Bit | 224 = 16 MByte |

| Vesa-Local-Bus | 32 Bit, direkt an die CPU gekoppelte Erweiterung | ||

| PCI 2.0 | 32 Bit (32 Signalleitungen): 33 MHz Taktfrequenz, CPU-unabhängig (1993; 133 MByte/s Datentransferrate, 5 V Signalspannung) | ||

| PCI 2.1 bis 2.3, 3.0 | 64 Bit: 66 MHz Taktfrequenz, max. 528 MByte/s Datentransferrate, 3,3 V Signalspannung ab PCI 2.2 | ||

| PCI-X 1.0 ... 2.0 64-Bit-Version von PCI Conventional |

PCI-X66: 533 MByte/s, max. 4 Geräte am Bus PCI-X100: 800 MByte/s, max. 2 Geräte am Bus PCI-X133: 1.066 MByte/s, max. 1 Gerät am Bus PCI-X266: 2.133 MByte/s, (PCI-X DDR) |

||

| PCI Express (PCIe) | serielle Punkt-zu-Punkt-Verbindung (kein paralleler

Bus)Datenübertragung erfolgt über so genannte Lanes (Spuren, Wege),

jede Lane besteht aus jeweils einem Leitungspaar für Senden und Empfangen 3,97 GByte/s (PCI-X533) 9,53 GByte/s je Richtung (PCI Express mit 32 Leitungspaaren) |

||

| AGP | AGP 1x: 32-Bit-Bus, 66 MHz, 266 MByte/s AGP 2x (533 MByte/s), AGP 4x (1.066 MByte/s) und AGP 8x (2.133 MByte/s) |

||

| Serial ATA (S-ATA) | serielle Punkt-zu-Punkt-Verbindung (Kabel mit 7 Leitungen) 1.0: 150 MByte/s; 2.0: 300 MByte/s |

||

PCI-Versionen im Überblick*

| PCI-Version | PCI 2.0 | PCI 2.1 | PCI 2.2 | PCI 2.3 | PCI-X-1.0 | PCI-X-2.0 | PCIe |

| Max. Busbreite (Bit) | 32 | 6 | 64 | 64 | 64 | 64 | |

| Max. Taktrate (MHz) | 33 | 66 | 66 | 66 | 133 | 4x133 | |

| Max. Bandbreite (GByte/s) | 0,12 | 0,5 | 0,5 | 0,5 | 0,99 | 3,97 | 9,53 |

| Slots pro Bridge | 4 | 2 | 2 | 2 | 1 | 1 | |

| Spannung (Volt) | 5 | 5/3,3 | 5/3,3 | 3,3 | 3,3 | 3,3/1,5 | |

| Einführung (Jahr) | 1993 | 1994 | 1999 | 2002 | 1999 | 2002 | 2003 |

Quelle: http://www.tecchannel.de

* Stand 08/2006

Alle Peripheral Component Interconnect (PCI) -Standards werden ständig überarbeitet und

weiterentwickelt. Diese Aufgabe obliegt dem PCI-SIG-Konsortium (http://www.pcisig.com/home), das die daraus

resultierenden Spezifikations-Updates auch veröffentlicht.

Darüber hinaus gab und gibt es noch andere Bussysteme wie z.B. Micro-Channel (MCA) und EISA, die aber keine weite Verbreitung gefunden haben.

Weitere Bussysteme wie SCSI, USB, Wireless USB, eSATA (external serial ATA) sowie das ursprünglich als SCSI-Nachfolger entwickelte serielle Bussystem IEEE 1394 (FireWire 400), IEEE 1394a (i.Link) und 1394b (FireWire 800) finden in heutigen Computersystemen Verwendung (vgl. 4.5).

4.4 Arbeits- und Festwertspeicher

4.4.1 Arbeitsspeicher

Der Arbeitsspeicher (RAM, Random Access Memory) ist der Speicher eines Computers, auf den lesend und schreibend zugegriffen werden kann und in dem die Komponenten des Betriebssystems, die aktuell zur Abarbeitung anstehenden Teile der Anwendungsprogramme sowie Daten gespeichert sind.

Der Arbeitsspeicher ist eine Aneinanderreihung von Speicherzellen, von denen jede mit Hilfe einer Nummer angesprochen werden kann (sog. Adressen). Das Steuerwerk ist in der Lage, mit Hilfe einer Adresse jede beliebige Speicherzelle gezielt anzusprechen.

Eine Speicherzelle besteht aus einzelnen Bits. Ein Bit kann zwei verschiedene Informationen aufnehmen (0 oder 1).

Bauarten

RAM-Bausteine sind Halbleiterbausteine, die u.a. in den Varianten DRAM (dynamisches RAM), FPM-DRAM, EDO-DRAM, VRAM, SRAM (statisches RAM), SDRAM, SLDRAM, RDRAM (Rambus), DDR-, DDR2 u. DDR3-SDRAM... hergestellt werden.

Bauformen sind hierbei SIP, SIM (30 Pins), PS/2-SIMM (72 Pins), DIMM (168 bzw. 184 Pins), RIMM (184 Pins, Rambus) sowie weitere (Spezial)-Formen, z.B. für (Laser-)Drucker.

4.4.2 Festwertspeicher

Read-Only Memory (abgekürzt ROM; Nur-Lese-Speicher), ein halbleiterbasierter Speicher, der Anweisungen oder Daten enthält, die gelesen, aber nicht mehr verändert werden können.

Auf diesem Speicher befinden sich Daten und Befehle, die beispielsweise beim Start des Computers verwendet werden können (z.B. BIOS soweit nicht als Flash-ROM (Flash-EEPROM) ausgeführt).

4.5 Input-Output-Schnittstellen

Die Schnittstellen werden über die Input-Output-Ports (IO-Ports) der Chipsätze des Motherboards gesteuert.

Für die Verbindung des Computers mit der "Außenwelt" stehen viele Möglichkeiten zur Verfügung:

Serielle (COM) und parallele (LPT) Schnittstelle, Monitor (VGA, DVI, HDMI), PS/2, USB, Gameport, Soundein- und -ausgabe, IEEE 1394 und 1394b, LAN, W-LAN, eATA, IrDA, Bluetooth...